# Release Notes

## 4.4.0

Released on December XXth, 2025.

### Release Notes

#### Linty Server

* Add the related clock domains for resets to the Reset report.

#### [Linty HDL Designer (VS Code extension)](https://marketplace.visualstudio.com/items/LintyServices.linty-hdl-designer/changelog)

* Improve the performance of report generation.

### Upgrade Notes

* If you have custom plugins, [update the destination path of the mounted volume](install.md#add-additional-plugins).

## 4.3.1

Released on November 28th, 2025.

### Release Notes

#### Linty Server

* Prevent overly long file names in reports that could cause crashes on certain file systems.

* Upgrade to the latest version of linty-graphviz for improved HTML report generation.

### Upgrade Notes

* You can continue running analyses with linty-scanner 4.3.0 (no changes required).

## 4.3.0

Released on November 25th, 2025.

### Release Notes

#### Linty Server

* 28 new rules for SystemVerilog.

* Add latches to report.

* Built on SonarQube Community Build 2025.11.

#### [Linty HDL Designer (VS Code extension)](https://marketplace.visualstudio.com/items/LintyServices.linty-hdl-designer/changelog)

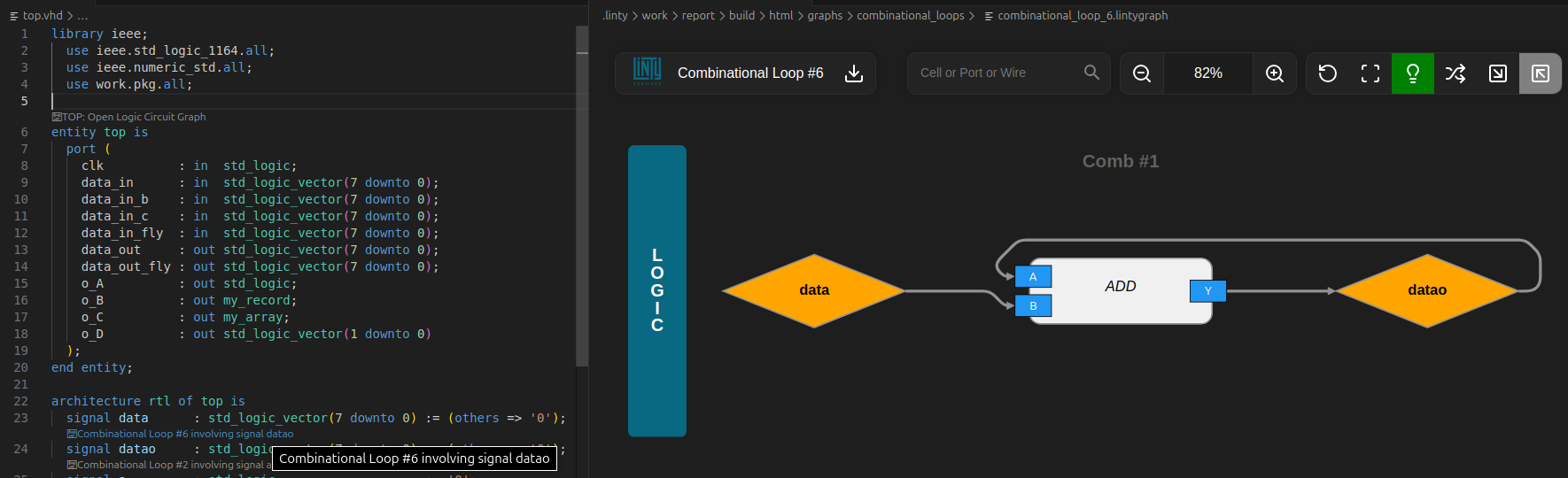

* Add CodeLens to display CDCs, RDCs, and combinational loops directly in the source code. Include clickable links that open the corresponding logic circuit graphs and design graphs.

#### [Linty Graph Visualization (VS Code extension)](https://marketplace.visualstudio.com/items/LintyServices.linty-graphviz/changelog)

* Improve highlighters.

* Hide/Show cells and wires by clock domain.

* Highlight cells and wires connecting selected elements.

### Upgrade Notes

* Rule _VERILOG030 - All case items should be different_ has been removed. Activate rule VERILOG2145 - Duplicated items in case statement should be removed instead.

## 4.2.0

Released on November 5th, 2025.

### Release Notes

* Advanced visualization of logic circuits as intuitive graphs. Optimized display for effortless human comprehension.

Logic flow clearly presented from inputs, through alternating combinational logic and flip-flops, all the way to

outputs. Clocks and resets neatly positioned at the bottom of the graph (with expandable/collapsible sections).

Input/output cones, direct source code access, sub-graph extraction, seamless navigation across sub-modules, and more.

* Integration with [VSG (VHDL Style Guide)](https://vhdl-style-guide.readthedocs.io/en/latest/index.html) to

check

formatting and indentation.

* All configuration files are now centralized in a dedicated `.linty` directory.

* Built on SonarQube Community Build 2025.10

### Upgrade Notes

Remove existing `.linty` directory.

Rename and move existing configuration files (`sonar-project.properties`, `read.ys`, `hierarchy.ys`, `slang.conf`) to a

dedicated newly created `.linty` directory. See:

* [Linty configuration](scan.md#base-configuration)

* [BugFinder configuration](scan_bugfinder.md#configuration)

* [slang configuration](scan.md#verilog-systemverilog-only)

* [Add `-Dproject.settings=".linty/linty.properties"` to the Docker command scanning your source code](scan.md#run-linty-scan)

In VS Code, update the path to the Linty report:

Ctrl + Shift + P + `Preferences: Open Settings (UI)`

Update `Live Preview: Server Root` property to `.linty/work/report/build/html`.

## 4.1.1

Released on June 3rd, 2025.

### Release Notes

* Fixes an issue while generating CDC and RDC graphs

* Takes into account VHDL trailing comments for descriptions in documentation

### Upgrade Notes

Keep using linty-scanner 4.1.0 to run analyses.

## 4.1.0

Released on May 28th, 2025.

### Release Notes

* [New reporting (HTML or VS Code) with new dynamic graphs: Design Hierarchy, Clock Hierarchy, Reset Hierarchy](./html_report.md)

* Built on SonarQube 2025.3

* New rules:

* HDL1034 - A clock domain should not use both rising and falling edges

* HDL1046 - An instantiation should not use too many global reset domains

* HDL1047 - A flip-flop should have a reset

### Upgrade Notes

#### Rules now applying to VHDL, Verilog/SystemVerilog and mixed language designs

The following rules now apply to VHDL, Verilog/SystemVerilog and mixed-language designs:

* VHDL1010 => HDL1041 - Falling should be preferred over rising to detect clock transitions

* VHDL1011 => HDL1042 - Rising should be preferred over falling to detect clock transitions

* VHDL1027 => HDL1035 - Active-high resets should be preferred over active-low resets

* VHDL1028 => HDL1036 - Active-low resets should be preferred over active-high resets

* VHDL1029 => HDL1037 - Synchronous resets should be preferred over asynchronous resets

* VHDL1030 => HDL1038 - Asynchronous resets should be preferred over synchronous resets

* VHDL1031 => HDL1039 - A reset domain should not use both asynchronous and synchronous resets

* VHDL1032 => HDL1040 - A reset domain should not use active-high and active-low resets

* VHDL1034 => HDL1044 - Each process and "always" block should use one reset domain maximum

* VHDL1049 => HDL1045 - An instantiation should not use too many clock domains

* VHDL1063 => HDL1043 - Latches should be removed

Activate corresponding HDL rules if some of these VHDL rules were activated in your VHDL quality profiles.

#### Linty Scanner

Upgrade linty-scanner to 4.1.0

#### Linty HDL Designer (VS Code extension)

Upgrade Linty HDL Designer to 4.1.0

## 4.0.1

Released on March 18th, 2025.

### Release Notes

It fixes the following issues:

* Not possible to render design hierarchy graph with blackboxes

* Issues are not always displayed in Linty HDL Designer on Windows

### Upgrade Notes

* Keep your current version of the linty-scanner: 4.0.0

* Upgrade Linty HDL Designer to 4.0.4

## 4.0.0

Released on December 17th, 2024.

### Release Notes

* Reset domain crossings (RDC) detection

* Fully rewritten Verilog/SystemVerilog plugin:

* Parses all standards

* Runs much faster

* Adds 136 new rules, most of which are included in the free version

of Linty HDL Designer

* Rules and reports on FSM now also apply to Verilog and mixed-language projects

* Built on SonarQube 10.7

#### New rules

145 new rules:

* HDL: 8 new rules on reset

domains, RDC, input port registration, etc.

* VHDL: 1 new rule on not

using reserved words in future VHDL standards as identifiers

* Verilog/SystemVerilog: 136 new rules

on implicit casts and conversions, overflows and many more

### Upgrade notes

The following rules now apply to VHDL, Verilog/SystemVerilog and mixed-language designs:

* VHDL1057 => HDL1016 - The number of reset domains per design should be as low as possible

* VHDL1058 => HDL1018 - All global resets should be generated within a unique reset management module

* VHDL1059 => HDL1020 - Reset management modules should comply with a naming convention

* VHDL1060 => HDL1019 - Clock management module and reset management module should be the same module

* VHDL1007 => HDL1023 - Track finite state machines (FSM)

* VHDL1020 => HDL1024 - FSM should have a minimal number of states

* VHDL1019 => HDL1025 - FSM should not have too many states

* VHDL1021 => HDL1026 - FSM should not have too many output signals

* VHDL1022 => HDL1027 - FSM should not have too many input signals

* VHDL1003 => HDL1028 - FSM state signal names should comply with a naming convention

* VHDL1023 => HDL1029 - FSM should not have states that can target too many other states

Activate corresponding HDL rules if some of these VHDL rules were activated in your VHDL quality profiles.

## 3.1.0

Released on May 18th, 2024.

### Release Notes

This release focuses on architecture with new rules and design hierarchy graph in

Linty HDL Designer. It also provides the ability to

generate documentation as HTML.

!Design Hierarchy

Built on SonarQube 10.5.1.

#### New rules

* VHDL316 - An entity should not have too many ports

* VHDL317 - A function or procedure should not have too many parameters

* VHDL318 - Generics should not define default values

* VHDL1073 - All assertions failing as note should be reviewed

* VHDL1074 - All assertions failing as warning should be reviewed

* VHDL1075 - All assertions failing as error should be reviewed

* HDL1012 - A module should not depend on too many other modules

* HDL1015 - Clock management module should be instantiated in top module

#### Rules that now apply to VHDL, Verilog/SystemVerilog and mixed-language designs

* VHDL1055 => HDL1013 - All clocks should be generated within a unique clock management module

* VHDL1056 => HDL1014 - Clock management module should comply with a naming convention

### Upgrade Notes

Activate HDL1013

and HDL1014

to replace removed VHDL1055 and VHDL1056 rules.

## 3.0.0

Released on February 8th, 2024.

### Release Notes

Linty detects all clock domain crossings (CDC). You can now easily browse, investigate, accept or fix any clock domain

crossing.

!img.png

Built on SonarQube 10.3.0.

#### New rules

* HDL1000 - All clock domains should be reviewed

* HDL1001 - All clock domain crossings should be reviewed

* HDL1004 - Top-level input ports should not be used within multiple clock domains

#### Rules that now apply to VHDL, Verilog/SystemVerilog and mixed-language designs

A new language has been created: HDL. HDL rules apply to

VHDL, Verilog/SystemVerilog and mixed-language designs.

The following rules have been extended to apply to VHDL and Verilog/SystemVerilog and mixed-language designs.

You should activate those rules in replacement of the related (and removed) VHDL/Verilog rules:

* VHDL1054 => HDL1002 - The number of clock domains per design should be as low as possible

* VHDL1048 => HDL1003 - Combinatorial loops should be removed

* VHDL1000 => HDL1005 - All input ports should be connected

* VHDL1001 => HDL1006 - All output ports should be connected

* VHDL1002 => HDL1007 - All inout ports should be connected

* VHDL1004 => HDL1008 - All output signals of top-level module should be registered

* VHDL1016 => HDL1009 - All output signals of low-level modules should be registered

* VHDL1017 => HDL1010 - Output signals should not be constant

* VHDL1018 => HDL1011 -Ports should not be directly connected

* VHDL177 and VERILOG007 => HDL001 - Files should contain an empty new line at the end

* VHDL179 and VERILOG006 => HDL002 - End-line characters should be consistent

* VHDL178 and VERILOG010 => HDL003 - Lines should not end with trailing whitespaces

* VHDL034 and VERILOG011 => HDL004 - Tabulation characters should not be used

* VHDL017 and VERILOG009 => HDL005 - Lines should not be too long

#### Linty Scanner adds compatibility to Windows and Mac

Linty analyses can now be run from Linux, Windows and Mac machines

built on AMD, Intel or ARM processors.

### Upgrade Notes

Please, ask for a new license key before upgrading to this latest version.

## 2.1.0

Released on November 25th, 2023.

### Release Notes

You can now check more than 200 rules on your VHDL code.

Built on the latest SonarQube 10.3.0.

#### VHDL

12 new rules have been added:

* VHDL1063 - Latches should be removed

* VHDL1064 - Choices outside of range should be removed

* VHDL1065 - Choices should not overlap

* VHDL1066 - Objects of different lengths should not be compared

* VHDL1067 - Range should not be empty

* VHDL1068 - Functions should always return a value

* VHDL1069 - Signals and variables should be assigned a value before being used

* VHDL1070 - Clock names should not contain frequency information

* VHDL305 - "while" loops should not be used for synthesis

* VHDL306 - Only one single architecture per entity should be defined

* VHDL307 - Code should be properly commented

* VHDL308 - Variables should not be used

VHDL187 has been split into three rules to allow different naming conventions for `for`, `if` and `case` generate

statements:

* VHDL187 - "for" generate statement labels should comply with a naming convention

* VHDL309 - "if" generate statement labels should comply with a naming convention

* VHDL310 - "case" generate statement labels should comply with a naming convention

Browse all new rules.

### Upgrade Notes

* VHDL168 rule has been removed. Activate its replacement that is able to deal with

ranges: VHDL1065 - Choices should not overlap

## 2.0.0

Released on September 19th, 2023.

### Release Notes

Linty now fully supports multi-language (VHDL and Verilog/SystemVerilog) projects.

Built on the latest SonarQube 10.2.0

version with support of Clean Code attributes.

#### VHDL

10 new rules have been added, most of them around clock and reset domains:

* VHDL1054 - The number of clock domains per design should be as low as possible

* VHDL1055 - All clocks should be generated within a unique clock management module

* VHDL1061 - Clock names should be preserved across the design

Browse all new rules.

### Upgrade Notes

* Request a new [license key](./configure.md#set-linty-license-keys") before upgrading

* Update the following property keys if you set them for some of your projects:

* `sonar.vhdl.topLevelEntity` => `sonar.hdl.topModule`

* `sonar.vhdl.file.simulationPaths` => `sonar.hdl.file.simulationPaths`

* `sonar.vhdl.yosys.hierarchyScriptPath` => `sonar.bugfinder.hierarchyScriptPath`

* `sonar.vhdl.yosys.readScriptPath` => `sonar.bugfinder.readScriptPath`

* `sonar.vhdl.yosys.workdir` => `sonar.bugfinder.workdir`

## 1.2.0

Released on July 4th, 2023.

### Release Notes

Built on the latest SonarQube 10.1.0

version.

It is now possible to [add custom plugins to the Linty platform](./install.md#add-additional-plugins).

#### VHDL

Linty VHDL now highlights, in gray, pieces of code that are not synthesized, adds four new rules:

* VHDL1050 - Unused entities should be removed

* VHDL1051 - Unused architectures should be removed

* VHDL1052 - Unused generate blocks should be removed

* VHDL1053 - A signal should not be used as both a reset and an enable

and improves existing rules with knowledge of unused code.

#### Verilog

This version integrates BugFinder for Verilog with its first

rule: VERILOG1000 - Unused modules should be removed

and adds design graph of each module.

### Upgrade Notes

Split your `build.ys` file into `read.ys` and `hierarchy.ys`. Replace `read -vhdl `

with `verific -vhdl `. See [Scan Your Code](./scan.md#with-bugfinder-and-linter) for further details.

Two distributions of the linty-server Docker image are now available:

* Based

on SonarQube Community Edition without branch and pull request support

* Based

on SonarQube Developer Edition with branch and pull request support

## 1.1.0

Released on April 26th, 2023.

### Release Notes

Built on the latest SonarQube 10.0.0

version.

#### VHDL

This version adds two new rules:

* VHDL1048 - Combinatorial loops should be removed

* VHDL1049 - An entity should not use multiple clocks

And generates graphical representations of the design. It is nice, for instance, to easily spot combinatorial loops.

### Upgrade Notes

Follow [upgrade guide](./install.md#upgrade-linty).

## 1.0.0

Released on March 9th, 2023.

### Release Notes

First official release of the Linty Server as Docker image.

#### VHDL

This version includes [BugFinder](./scan_bugfinder.md), a new powerful engine to detect bugs based on synthesized code

analysis. BugFinder rules are tagged as `bug-finder`).

There are 47 of them in this first version. Here are some of them:

* VHDL1001 - All output port of an entity should be connected

* VHDL1004 - All output signals of top-level entity should be registered

* VHDL1017 - Output signals should not be constant

Browse all of them on our demo instance.

Lots of rules have been added or improved. Some rules also changed ID because they were re-implemented with BugFinder.

Thus, we highly recommend you to review your quality profile(s) to (re)activate and configure new rules.